AND6: A Deep Dive into the 6‑Input CMOS AND Gate

As electronic devices become more advanced, integrating complex logic into a single component becomes essential. Enter AND6, a 6‑input AND gate fabricated in a 0.6 µm CMOS process by ETC/Austria Mikro Systeme. Simple yet powerful, AND6 offers low power usage, efficient die area, and versatile application potential in digital circuits.

In this guide, we’ll explore what makes AND6 special, review its technical highlights, and show you how to use it efficiently in your next electronics project. Whether you’re a hardware engineer or an electronics hobbyist, you’ll find plenty of practical insights ahead.

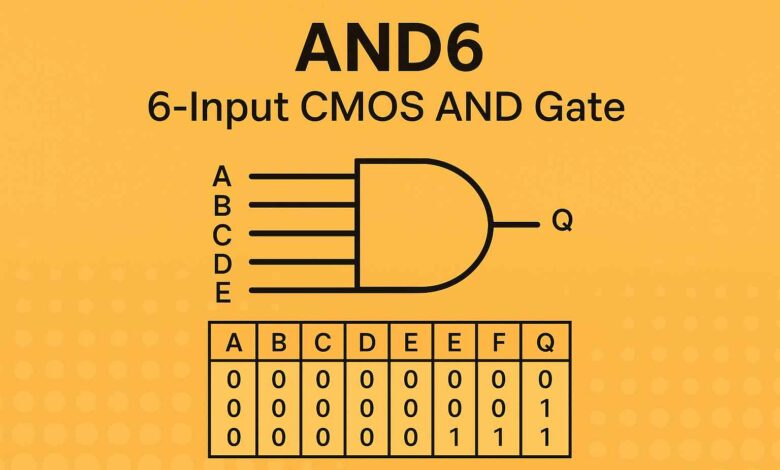

What Is AND6?

AND6 is a logic IC that outputs a HIGH (1) only when all six inputs (A–F) are HIGH. If any input is LOW (0), the output goes LOW. Built using 0.6 µm CMOS technology, it features:

- 1× drive strength

- Die area: ≈ 1.08 mils²

- Power consumption: ≈ 2.83 µW per MHz Wiring Diagrams Hub: Your Complete Guide+4Scribd+4Alldatasheet+4Datasheet4U

It’s designed for compact, energy-efficient logic operations.

How AND6 Behaves: Truth Table & AC Specs

Truth Table

| A | B | C | D | E | F | Q |

|---|---|---|---|---|---|---|

| 0 | X | X | X | X | X | 0 |

| X | 0 | X | X | X | X | 0 |

| … | … | … | … | … | … | … |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

(Q = HIGH only when all inputs are HIGH) Wikipedia

AC Performance (Typical, @3.3 V, 25 °C)

- Propagation delay (tpd): ~0.5–2.6 ns depending on load

- Output slope times: ~0.7–7.5 ns Pinterest+8Scribd+8Datasheet4U+8

Ideal for moderately fast digital systems.

Where to Use AND6

1. Signal Interlock Systems

Combine six sensor or control signals into a single logic output. Great for safety or coordination mechanisms.

2. Programmable Logic Arrays (PLAs)

Use AND6 as one product term in larger logic expressions, helping to build complex functions.

3. Gate Expansion

Need more inputs than a standard 2– or 4–input gate? AND6 saves space when you need exactly 6 inputs.

4. Power-Efficient Design

Its low power usage (≈2.83 µW/MHz) makes it perfect for battery-powered and low-energy applications YouTube+9Wiring Diagrams Hub: Your Complete Guide+9Google Cloud Storage+9Google Cloud Storage+8Scribd+8Datasheet4U+8datasheet.hk+1Datasheet4U+1.

Practical Design Tips

A. Drive Strength

AND6 has only 1× drive, so buffer it (e.g., with a CMOS buffer) if you’re driving multiple gates or heavy loads.

B. Level Compatibility

Designed for 3.3 V. If used at 5 V or 1.8 V, check the datasheet for voltage tolerance—or consider a level-translating buffer.

C. Load Management

Propagation delay increases with load capacitance; mitigate with proper decoupling and short PCB traces.

D. Thermal Considerations

Although low-power, distribution of power and heat still matters. Keep power rails stable and layout traces thoughtfully.

E. Pin Assignment & Layout

Use the datasheet to design PCB footprints with minimal crosstalk. CMOS gates perform best with clean signal routing.

Competing & Complementary Devices

AND6 is a niche solution compared to widely used series like 74xx or 40xx. If you need high-speed or TTL-level compatibility, you may consider:

- 74LS21 – Dual 4‑input AND, TTL

- 74HC11 – Triple 3‑input AND, CMOS

- 74HC30 – 8‑input NAND, CMOS

For compact logic, consider PLDs or FPGAs—but for simplicity and cost-efficiency, AND6 stands strong.

Quick Specs Snapshot

- Manufacturer: ETC / AMS

- Process: 0.6 µm CMOS

- Inputs: 6 (A–F)

- Output: Q = HIGH only when A–F are HIGH

- Die area: 1.08 mils² ebics.net+3Datasheet4U+3Alldatasheet+3Wikipedia+2futurlec.com+2Build Electronic Circuits+2Scribd+1Datasheet4U+1

- Power: ≈ 2.83 µW/MHz Scribd+1Datasheet4U+1

- Propagation delay: ~0.5–2.6 ns (varies by load)

- Slope times: ~0.7–7 ns

Designing with AND6: Example Use Case

Scenario: Interlocking sensors 1–6 to activate a machine only when all conditions are met (e.g., doors closed, safety limits reached)

Steps:

- Connect each sensor to one input (A–F).

- Tie output Q to a machine-enable logic line.

- Add a CMOS buffer downstream to drive your machine control circuits.

- Use decoupling capacitors (0.1 µF) close to the IC.

- Stay within the 3.3 V supply range (or buffer if needed).

- Route PCB traces carefully to minimize interference.

Result: The machine turns on only when all six sensors report an OK status, ensuring a safer operational flow.

Integrating AND6 in Compact Digital Designs

If your design requires many AND operations but limited pins, use AND6 to:

- Reduce component count (vs. using three 2‑input AND gates)

- Simplify PCB layout

- Achieve precise, low-power performance

It’s a smart choice for straightforward digital logic where high-channel density and power efficiency matter.

Test and Validation Tips

- Verify propagation delay under your board’s specific load.

- Monitor current draw across frequency ranges to confirm power spec.

- Check output signal slope with an oscilloscope for clean transitions.

- Test across temperatures (0–70 °C) to ensure reliable operation.

Final Thoughts

The AND6 gate is a compact, energy-efficient solution in digital logic design, making it easy to manage multiple conditions with minimal footprint. It’s perfect for applications needing:

- Six-way signal interlocks

- Low-power logic implementations

- Compact PCB layouts

While oversized for smaller logic problems, AND6 shines where simplicity, space, and efficiency count.

Join the Conversation!

Have you used AND6 in your project—or a similar multi-input logic chip? Share your experiences or questions in the comments below. If you found this guide helpful, please share it with your fellow electronics enthusiasts!

FAQ

1. What voltage does AND6 operate at?

AND6 is built for a 3.3 V supply in 0.6 µm CMOS. If you’re using different voltages, you may need level shifters.

2. Can I cascade two AND6 gates?

Yes—your output goes through a buffer before feeding another AND6 to maintain signal integrity.

3. How does AND6 compare to 74HC30?

While 74HC30 is an 8‑input NAND (requires inversion), AND6 is a 6‑input direct AND gate. Choose based on logic requirements and available ICs.

4. Is AND6 still produced?

It’s older tech—availability may be limited. Check distributors or consider equivalent 6‑input AND gates like the HCT series.

5. How to reduce propagation delay in my circuit?

Minimize capacitive loads, shorten traces, add decoupling, and buffer the outputs. This keeps delay in the lower nanosecond range.